10+ pll block diagram

4 CD4046B Phase-Locked Loop. Frequency is scaled by the use of counters.

2

The PLL structure consists of a low-power linear VCO and two.

. The u and υ axes have their origin at the centroid CFor the calculation assume all corners to be square. PLL Block Diagram Hardware Connections. In this case a super-fast.

VDD_LV_PLL Power PLL low voltage Supply 36 P4 VSS_LV_PLL Ground PLL low voltage Ground 35 N4 Table continues on the next page. As shown there is a vertical pin through the broad side of the waveguide that extracts the vertical polarisation signals as an electrical current. Solution for 10 mm 10 mm 50 mm T20 x.

March 2022 DS5319 Rev 18 1116 STM32F103x8 STM32F103xB Medium-density performance line Arm-based 32-bit MCU with 64 or 128 KB Flash USB CAN 7 timers 2 ADCs 9 com. MachXO3 Family Data Sheet - Lattice Semi. This is information on a product in full production.

RSL10 INTERNAL BLOCK DIAGRAM The block diagram of the RSL10 chip is shown in Figure 1. A Versatile Building Block for Micropower Digital and Analog Applications 3 CD4046B PLL Technical Description Figure 2 shows a block diagram of the CD4046B which has been implemented on a single monolithic integrated circuit. The input frequency range of the PLL is 10 to 40 MHz.

61 112017 NXP Semiconductors 5. Functional block diagram hp jack detection regulator input mixers alc microphone bias pll linn linp laux jackdetmicin rinp rinn raux micbias lhp loutn loutp adau1761 rhp monoout routp routn cm iovdd dgnd dvddout avdd avdd agnd output mixers dac digital filters adc digital filters dac adc dac adc sda cout i 2 cspi control port serial data. If CLKIN is 40 MHz the CLKIN input divider must be used to bring the PLL.

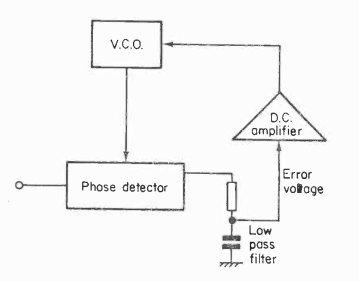

O To. Phase Locked Loops A PLL is a truly mixed-signal circuit involving the co-design of RF digital and analog building blocks. General Transceiver Block Diagram Although there are a variety of frequency synthesis techniques phase locked loop PLL represents the dominant method in the wireless communications industry.

In the example shown an ADF4xxx synthesizer is used with an external filter and VCO. All Lattice trademarks registered trademarks patents and disclaimers are as listed at www. Transistors consume more power since they are active components.

As we saw in the block diagram above there are a lot of elements preceding and following a Digital Signal Processor. A non-linear negative feedback loop that locks the phase. Stuff like filters and converters add to the complexity of a system.

CrossLink Family Data Sheet 2015-2022 Lattice Semiconductor Corp. Low noise block downconverter LNB diagram. System Block Diagram Introduction MPC5744P Data Sheet Rev.

Phase Locked Loop Block Diagram ÖN Ref Div Loop Filter VCO Phase Locked Loops PLL are ubiquitous circuits used in. The actual programming techniques required to synchronize the sample clocks of multiple boards through a phase-locked loop depends on the type of hardware in use. The Si5351 is a highly flexible and configurable clock generator and VCXO.

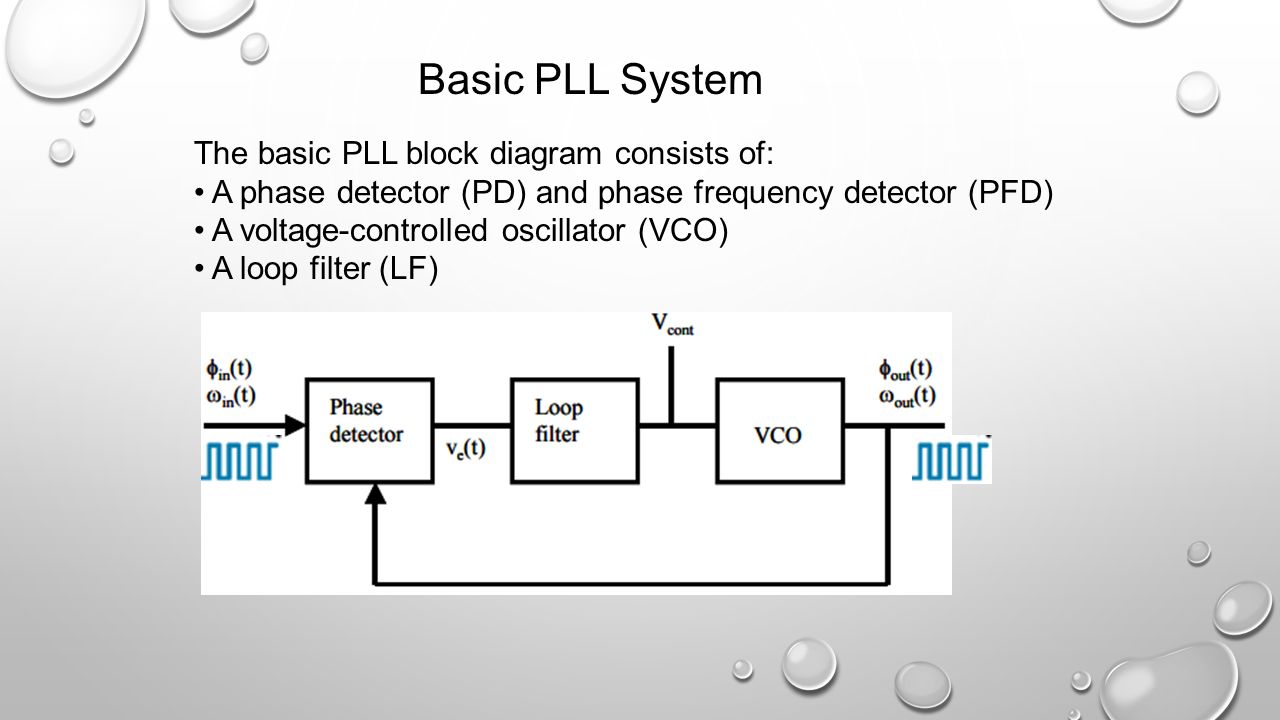

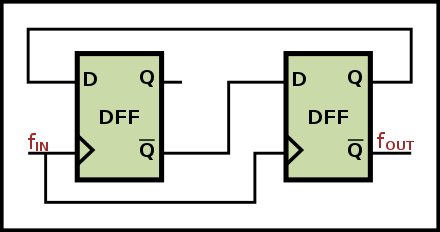

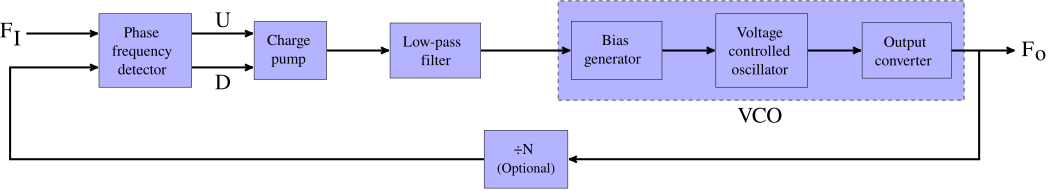

The block diagram of a PLL operating as a frequency synthesizer is shown in Figure 1 74 It consists of a reference oscillator OSC a phasefrequency detector PFD a charge pump CP a loop filter LF a voltage-controlled oscillator VCO and two frequency dividers FDs. Clock Data Recovery Equalizer. It consists of a reference oscillator OSC a phasefrequency detector PFD a charge pump CP a loop filter LF a voltage-controlled oscillator VCO and two frequency dividers FDs.

- Three crystalresonator modes up to 20 MHz - Three external clock modes up to 20 MHz Fail-Safe Clock Monitor. An external reference PLL uses a 10 MHz reference. The block diagram of a PLL operating as a frequency synthesizer is shown in Figure 1 8.

PLL like most wireless communication technologies is relatively new and has matured only in the last decade. 10 mnt -150 mm -150 mm Prob. - Accurate to 1 typical - Software selectable frequency range from 16 MHz to 250 kHz - PLL multiplier to 32 MHz 31 kHz Low-Power Internal Oscillator External Oscillator Block with.

Pinouts MPC5744P Data Sheet Rev. The diagram shows the input waveguide on the left which is connected to the collecting feed or horn. How do I minimize lock time.

16 MHz Internal Oscillator Block. Determine the distance y to the centroid of the area and then calculate the moments of inertia I u and I υ of the channels cross-sectional area. To support this flexibility Skyworks Solutions has created.

Balun Oscillators 32 kHz XTAL 48 MHz XTAL RC Oscillator EXT Clock IO Bluetooth Low Energy Radio Bluetooth 52 Arm Cortex M3 processor 32bit DualMAC DSP. With PCI-based products X Series PCI DAQ. A block diagram of the Si5351 programmable clock IC is shown in Figure 1.

High-Performance 10100 Ethernet Transceiver - Compliant with IEEE80238023u Fast. By increasing the PFD. The PLL is a feedback loop that wh en in lock forces.

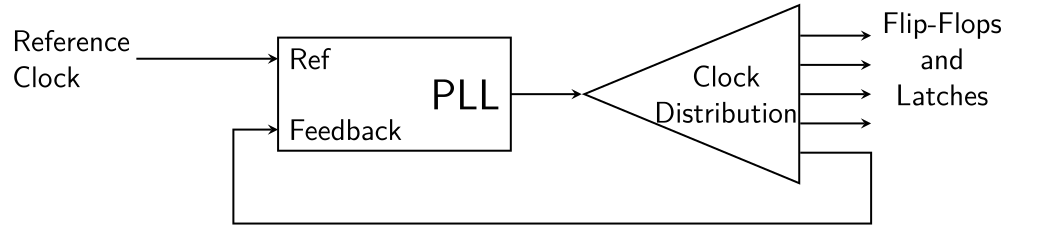

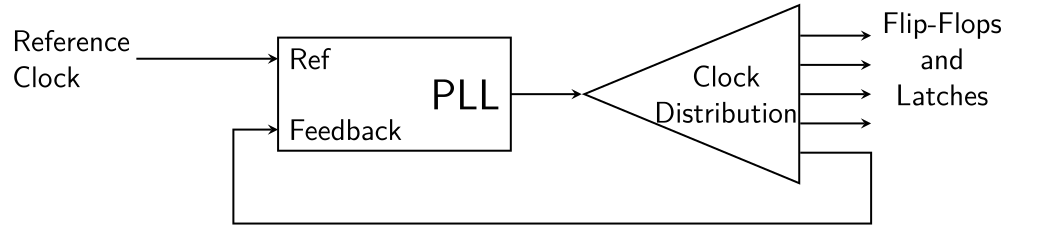

Figure 2 shows a block diagram of the PLL that is used on the M Series DAQ devices. Squeltch Filters Analog-to-Digital 10M RX Logic 100M RX Logic 100M PLL 10M PLL. A digital signal processor is made up of transistors.

Block diagram of a PLL. The PLL is a feedback loop that wh en in lock forces. This is information on a product in full production.

RSL10 Block Diagram Power Management Unit Antenna DCDC LDO Interface No ext. Niknejad PLLs and Frequency Synthesis. January 2022 DS12991 Rev 4 194 STM32G030x6x8 Arm Cortex-M0 32-bit MCU up to 64 KB Flash 8 KB RAM 2x USART timers ADC comm.

Review Part 2 Introduction Energy Harvesting Eh Energy Harvesting Also Known As Power Harvesting Or Energy Scavenging Is The Process In Which Energy Ppt Download

Lm567 Pll Tone Decoder Voltage Controlled Oscillator Electronics Projects Electronics Basics

Noc Block Diagram And Tile Architecture Download Scientific Diagram

Proposed Transceiver Block Diagram With Shaded Area Showing The Scope Download Scientific Diagram

Phase Locked Loop Wikiwand

Phase Locked Loop Wikiwand

Tracking Range Of Pll And Frequency Range Of Vco Versus Power Supply Download Scientific Diagram

Phase Locked Loop Wikiwand

Cy7c68013a Usb Microcontroller Datasheet Features And Block Diagram

Phase Locked Loop Wikiwand

2

Costas Loop Wikiwand

Frequency Synthesizer Wikiwand

How Does Vco In Pll In A Computer Processor Work Quora

Zisworks The X28 X39 Story

Simple Circuits Using Ic 7400 Nand Gates Homemade Circuit Projects

How Does Vco In Pll In A Computer Processor Work Quora